バージョン:2025/02/25

目次:

目的。

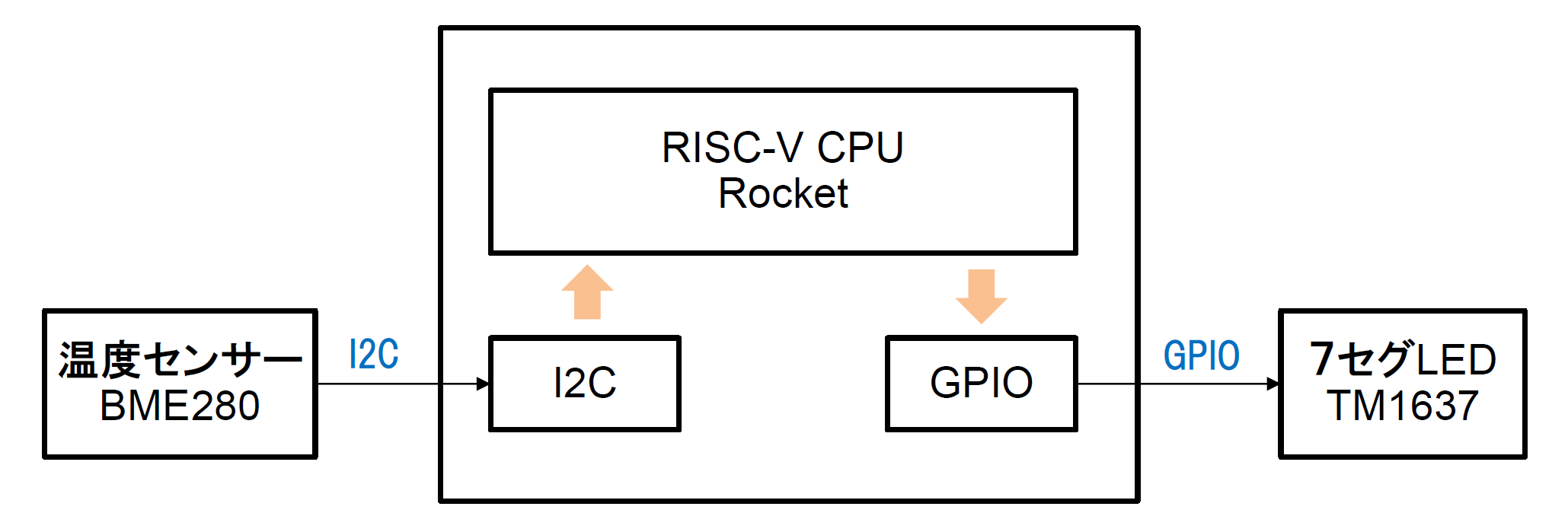

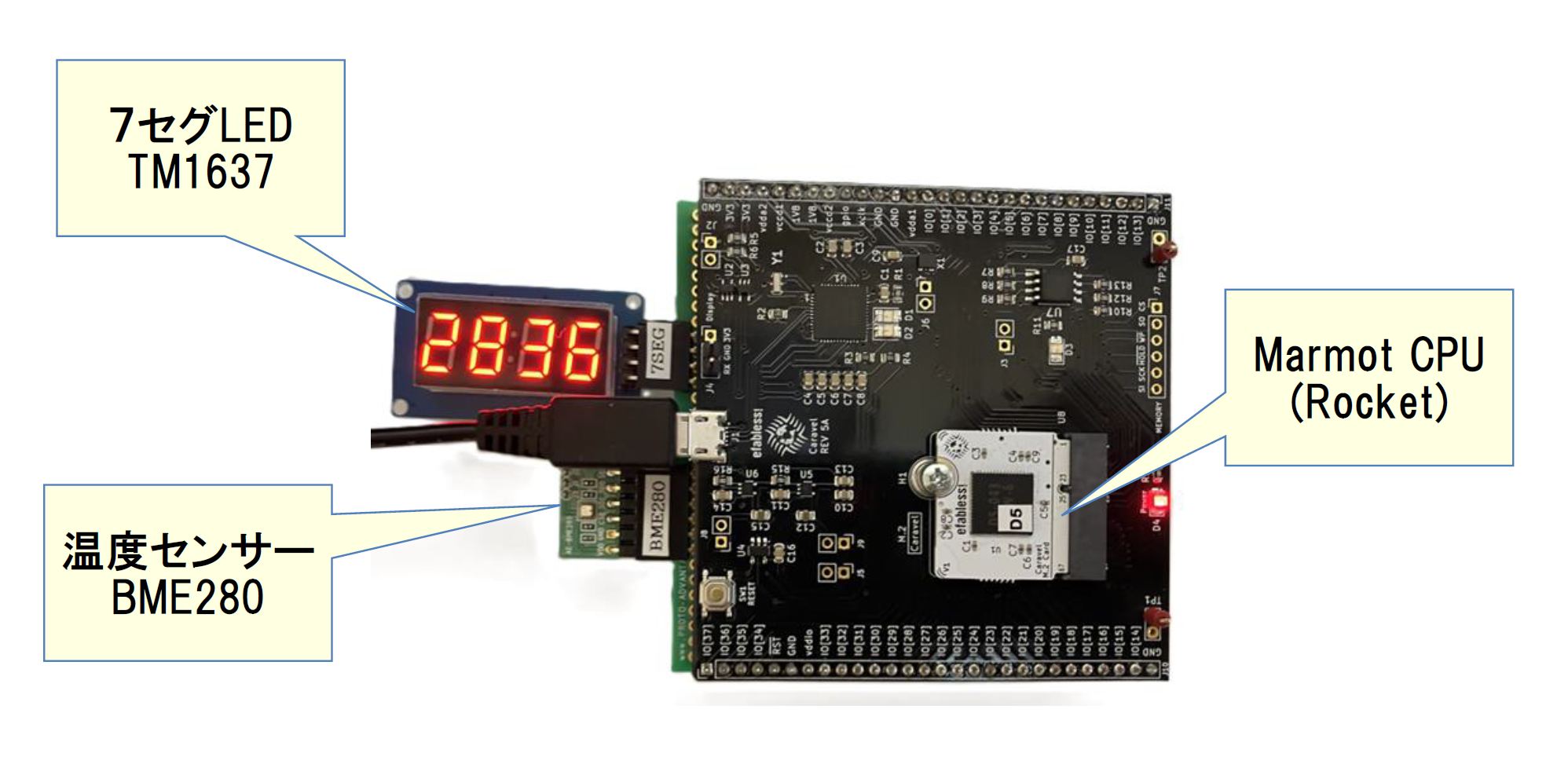

MarmotがサポートしているI2C, GPIO, SPI の動作の確認(今回、SPIは除外

処理内容

I2C0_REG(OC_I2C_PRER_LO) = 0x0f;

I2C0_REG(OC_I2C_PRER_HI) = 0x0;

I2C0_REG(OC_I2C_CTR) = OC_I2C_EN;

ピンクの線: プリスケーラーの設定

黄色の線: I2Cのイネーブル

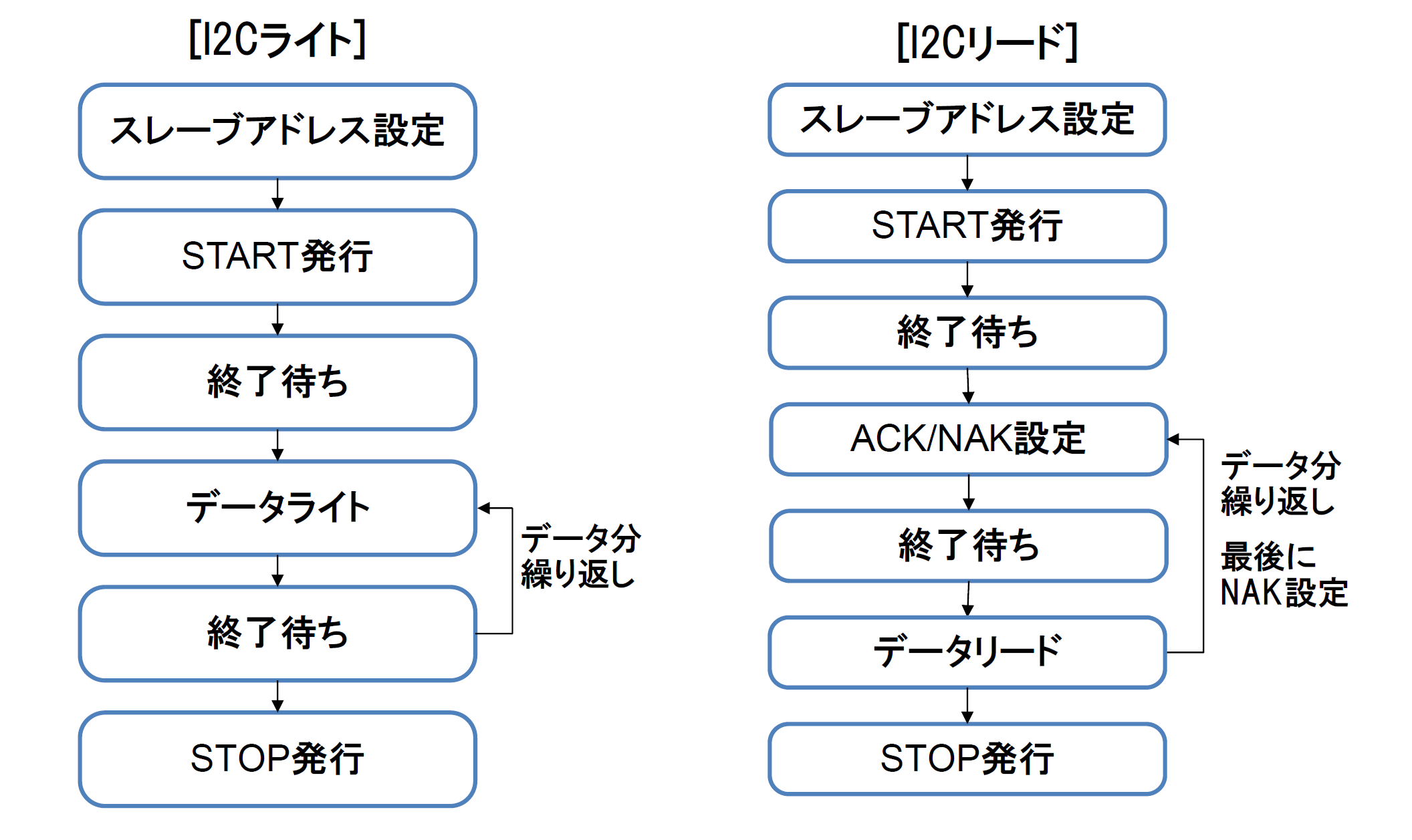

Marmot の I2Cライト・リード

| 資料 | 場所 |

|---|---|

| ドキュメント | https://www.bosch-sensortec.com/products/environmental-sensors/humidity-sensors-bme280 |

| サンプルコード | https://github.com/boschsensortec/BME280_SensorAPI |

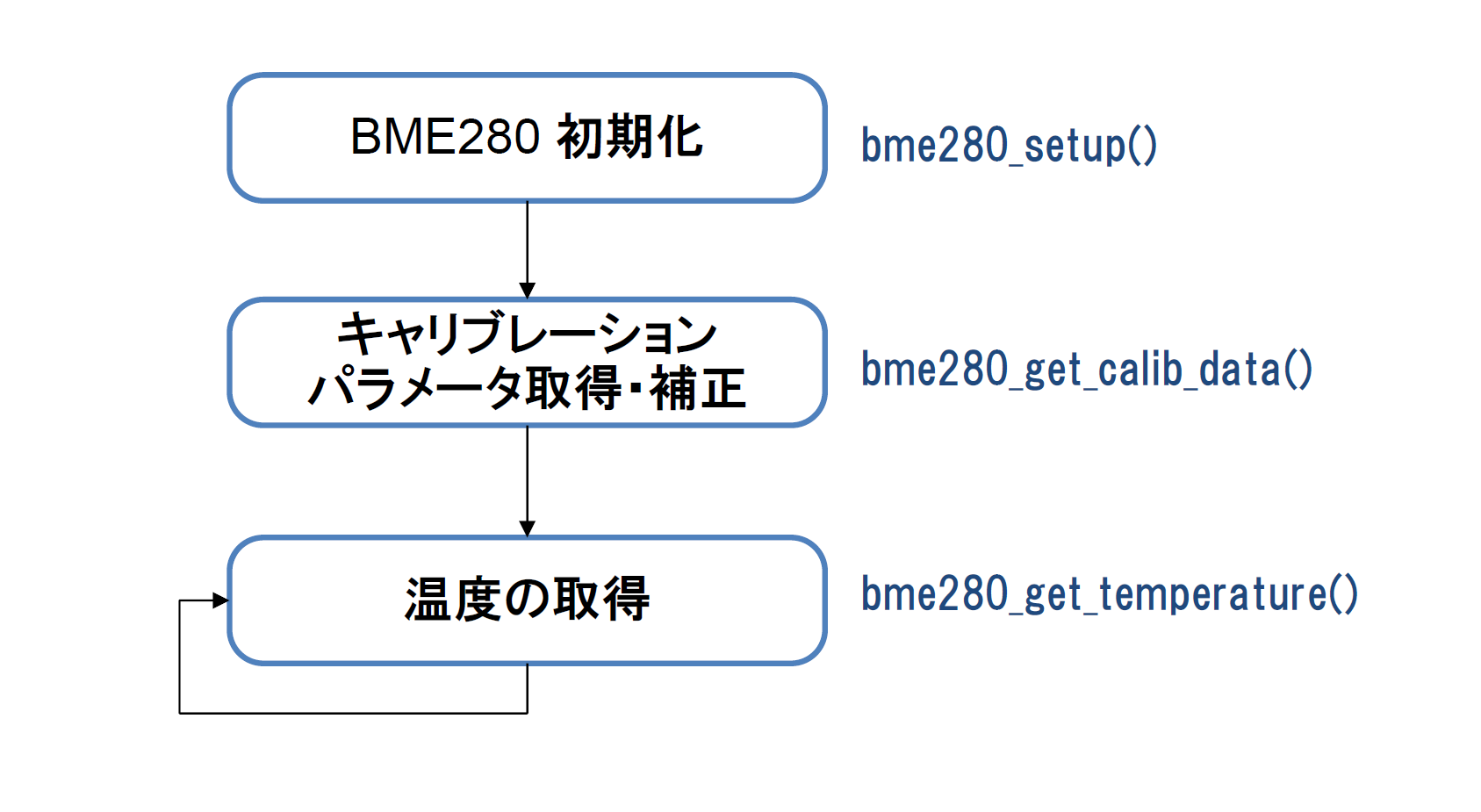

BME280の制御フロー

GPIOの仕様は、Freedom FE310 Manual

Chapter 10 Figure 10で確認

資料:以下に英語版が存在

https://github.com/revolunet/tm1637/blob/master/datasheet-en.pdf

特徴=> I2Cのようなオープンドレイン制御を想定?

Linuxでのgpio-i2c ドライバのような制御を行うGPIO に OE制御と出力データ設定のインタフェースを設定

reg_mprj_io_13 = GPIO_MODE_USER_STD_BIDIRECTIONAL; // IO3

reg_mprj_io_12 = GPIO_MODE_USER_STD_BIDIRECTIONAL; // IO2

reg_mprj_io_11 = GPIO_MODE_USER_STD_BIDIRECTIONAL; // IO1

reg_mprj_io_10 = GPIO_MODE_USER_STD_BIDIRECTIONAL; // IO0

SPIフラッシュ命令フォーマットレジスタ(ffmt)

| ビット | フィールド名 | 属性 | 初期値 | 説明 |

|---|---|---|---|---|

| 0 | cmd_en | RW | 0x1 | コマンド送信を有効化 |

| [3:1] | addr_len | RW | 0x3 | アドレスバイト数(0~4) |

| [7:4] | pad_cnt | RW | 0x0 | ダミーサイクル数 |

| [9:8] | cmd_proto | RW | 0x0 | コマンド送信時のプロトコル |

| [11:10] | addr_proto | RW | 0x0 | アドレスおよびパディング送信時のプロトコル |

| [13:12] | data_proto | RW | 0x0 | データ受信時のプロトコル |

| [15:14] | Reserved | |||

| [23:16] | cmd_code | RW | 0x3 | コマンドバイトの値 |

| [31:24] | pad_code | RW | 0x0 | ダミーサイクル中に送信する最初の8ビット |

例えば、以下のコードは SPI フラッシュの命令フォーマットレジスタを QPI モードで Fast Read を使用するように設定します。

// Set XIP access to Quad mode

dummy = SPI_INSN_CMD_EN

| SPI_INSN_ADDR_LEN(0x3)

| SPI_INSN_PAD_CNT(0x2)

| SPI_INSN_CMD_PROTO(SPI_PROTO_Q)

| SPI_INSN_ADDR_PROTO(SPI_PROTO_Q)

| SPI_INSN_DATA_PROTO(SPI_PROTO_Q)

| SPI_INSN_CMD_CODE(0x0b) // Fast read

| SPI_INSN_PAD_CODE(0x00);

while (_REG32(spi_base_addr, SPI_REG_RFMT) != dummy) {

_REG32(spi_base_addr, SPI_REG_RFMT) = dummy;

}

// Set SPI Flash to Quad mode

while (_REG32(spi_base_addr, SPI_REG_TXFIFO) & SPI_TXFIFO_FULL); // Wait until TX FIFO not full

_REG32(spi_base_addr, SPI_REG_TXFIFO) = CMD_ENTER_QUAD_MODE; // 0x38

注意: この関数はQSPIフラッシュではなく、ITIM(Instruction Tightly Integrated Memory)上で実行する必要がある。

__attribute__ ((section (".text_itim"))) void init_spi(uint32_t spi_base_addr)

{

volatile uint32_t dummy;

asm volatile ("fence\n\t"

"fence.i");

// Set SPI clock

while (_REG32(spi_base_addr, SPI_REG_SCKDIV) != SCKDIV) {

_REG32(spi_base_addr, SPI_REG_SCKDIV) = SCKDIV;

}

// Disable XIP mode

while (_REG32(spi_base_addr, SPI_REG_RCTRL) != 0x0) {

_REG32(spi_base_addr, SPI_REG_RCTRL) = 0x0;

}

// Set SPI Flash to Quad mode

while (_REG32(spi_base_addr, SPI_REG_TXFIFO) & SPI_TXFIFO_FULL); // Wait until TX FIFO not full

_REG32(spi_base_addr, SPI_REG_TXFIFO) = CMD_ENTER_QUAD_MODE;

// Set XIP access to Quad mode

dummy = SPI_INSN_CMD_EN

| SPI_INSN_ADDR_LEN(0x3)

| SPI_INSN_PAD_CNT(0x2)

| SPI_INSN_CMD_PROTO(SPI_PROTO_Q)

| SPI_INSN_ADDR_PROTO(SPI_PROTO_Q)

| SPI_INSN_DATA_PROTO(SPI_PROTO_Q)

| SPI_INSN_CMD_CODE(0x0b) // Fast read

| SPI_INSN_PAD_CODE(0x00);

while (_REG32(spi_base_addr, SPI_REG_RFMT) != dummy) {

_REG32(spi_base_addr, SPI_REG_RFMT) = dummy;

}

// Enable XIP mode

while (_REG32(spi_base_addr, SPI_REG_RCTRL) != SPI_FCTRL_EN) {

_REG32(spi_base_addr, SPI_REG_RCTRL) = SPI_FCTRL_EN;

}

}

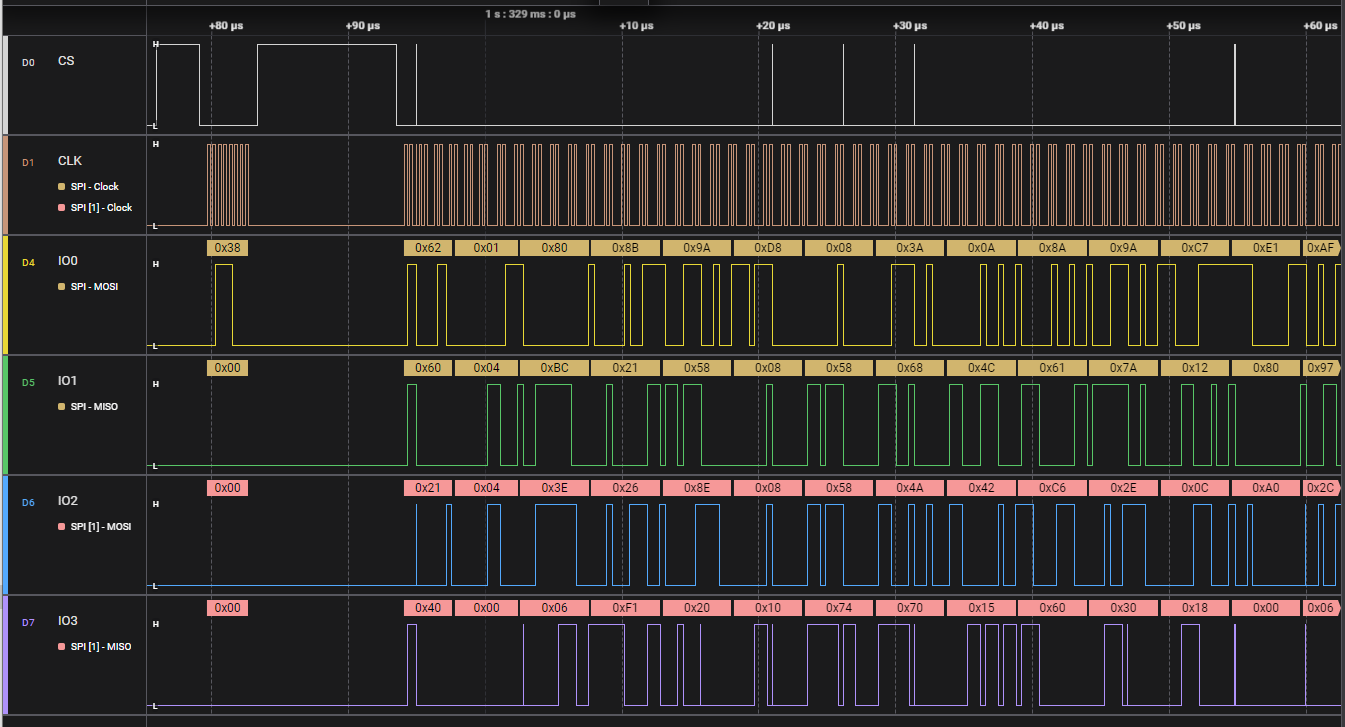

以下は、QSPI フラッシュを QPI モードで動作させた結果です。

Copyright © Japan Embedded Systems Technology Association All Rights Reserved.